verilog 延迟时间 超前进位加法器 |

您所在的位置:网站首页 › 假设所有门电路延迟均为t 为什么8位串行可控加减法器的时间延迟是18t › verilog 延迟时间 超前进位加法器 |

verilog 延迟时间 超前进位加法器

|

延迟时间:

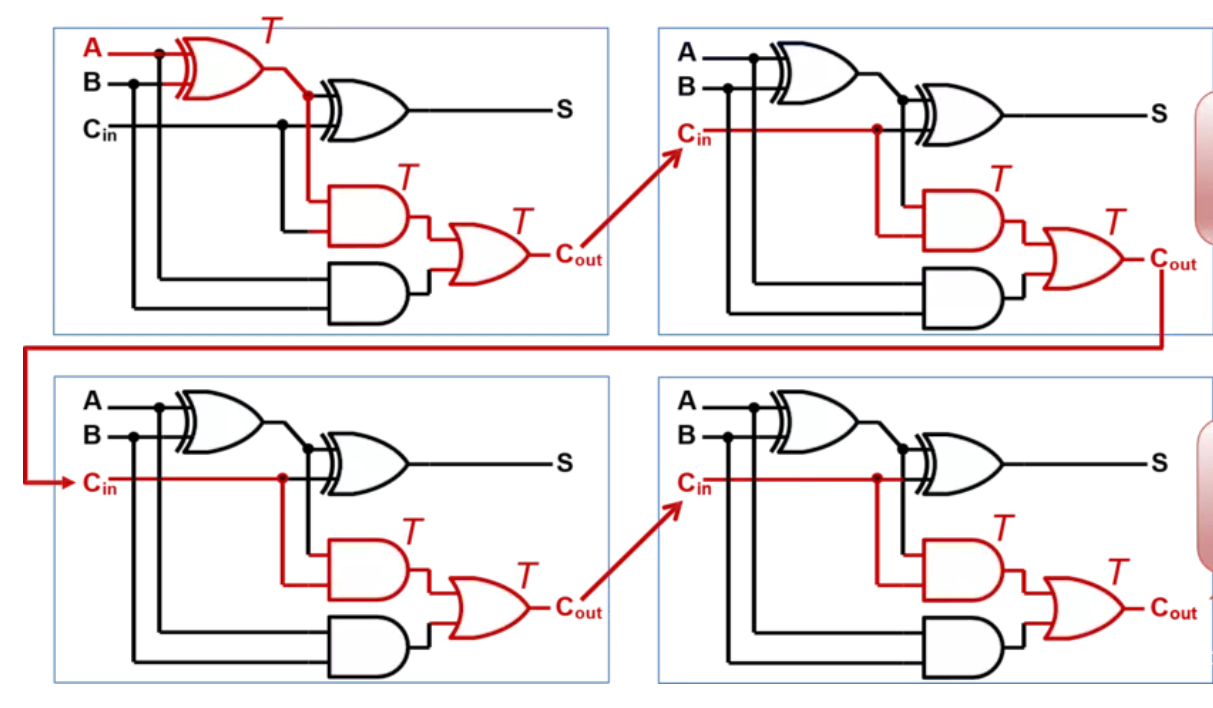

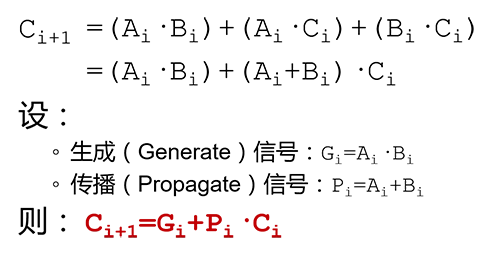

如图4位全加器,此类进位输出,像波浪一样,依次从低位到高位传递, 最终产生结果的加法器,也因此得名为行波进位加法器(Ripple-Carry Adder,RCA)。其关键路径如图中红线所示:假设经过一个门电路的延迟时间为T,则其延迟时间为(T+T)*4+T=9T。 串行的全加器,缺点相当明显,即加法器的延时过高,电路的工作频率低。 对于一个 n bit 的行波加法器,其延时为(T+T)*n+T=(2n+1)T。 超前进位加法器:超前进位加法器 (Carry-Lookahead Adder,CLA)是高速加法器,每一级进位有附加的组合电路产生。高位的运算不需要地位的等待,因此速度很高。 每一级的进位: 对于4 bit的加法器,每个进位如下,

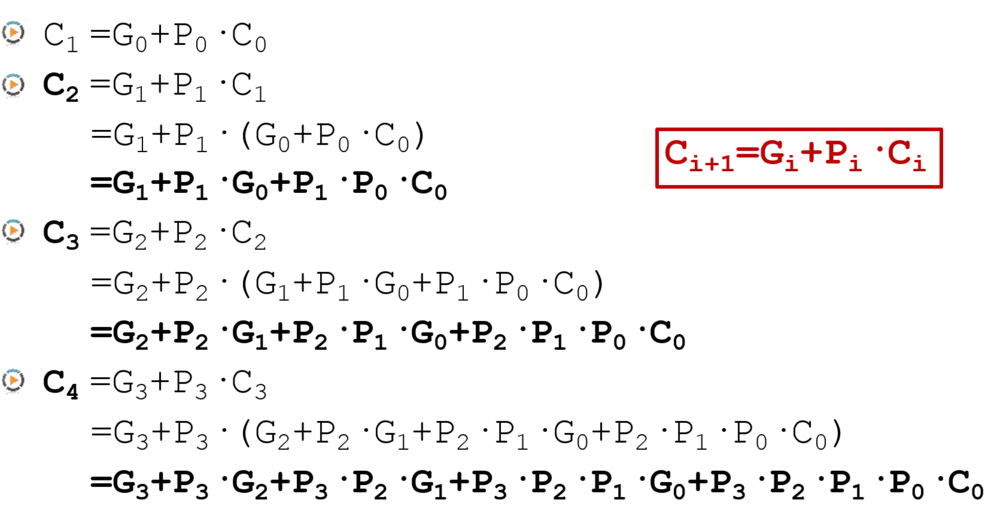

进位延时只有三个门的延时,加上最后一级全加器 sum = a ^ b ^ cin 的延时,即四个延时时间。

|

【本文地址】

可以看出,每个进位都不需要等待地位,直接计算可以得到。由此得到了提前计算进位输出的方法, 用这样的方法实现了加法器就被称为超前进位加法器。其组合电路如下:

可以看出,每个进位都不需要等待地位,直接计算可以得到。由此得到了提前计算进位输出的方法, 用这样的方法实现了加法器就被称为超前进位加法器。其组合电路如下:

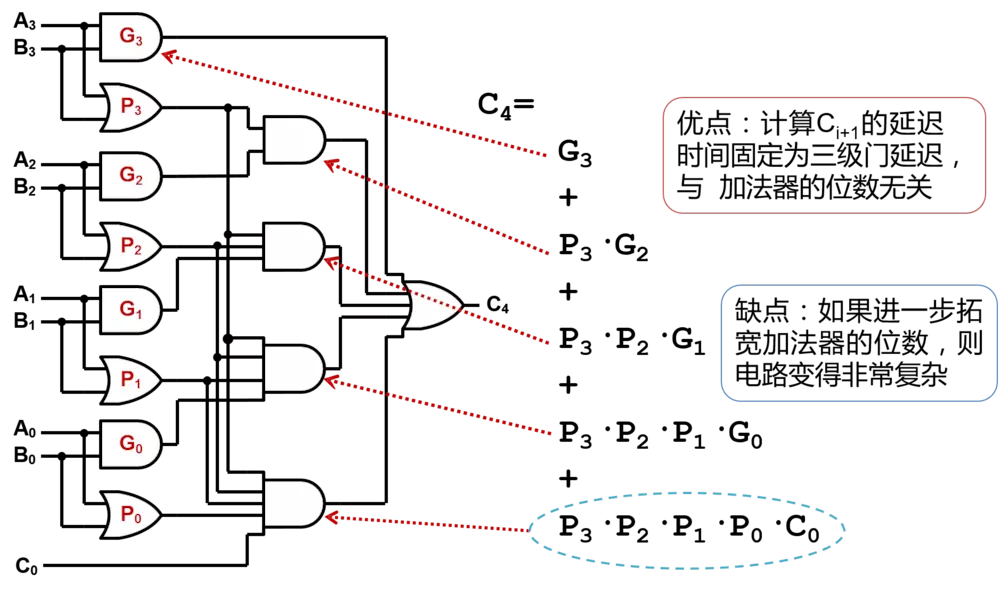

实现32位的完全的超前进位,电路就会变得非常的复杂。可采用多个小规模的超前进位加法器拼接而成一个较大的加法器,例如,用4个8-bit的超前进位加法器连接成32-bit加法器。

实现32位的完全的超前进位,电路就会变得非常的复杂。可采用多个小规模的超前进位加法器拼接而成一个较大的加法器,例如,用4个8-bit的超前进位加法器连接成32-bit加法器。